本篇主要是针对单bit信号的分析,关于多bit数据的CDC处理可参考异步fifo异步FIFO常用知识总结-CSDN博客

1.异步复位,同步释放

原理:复位信号同其他信号一样也有建立时间和维持时间的时序要求,称之为移除时间和恢复时间。recovery time(恢复时间)描述的是非复位信号在时钟上升沿到来前需要保持的最小时间;removal time(移除时间)描述的是复位信号在上升沿到来之后需要保持的最小时间。

由此可知,当复位信号不在时钟有效边沿变化时,可以保证电路的复位和恢复信号能被准确采样到。在实际设计中,有的模块先复位再给模块供应时钟,保证了复位信号与时钟错开,避免出现recovery 和removal违例的问题。

Q:为什么需要异步复位同步释放?

异步复位信号可以直接作为管脚引出,节约资源,时延缩短。在对于复位精度有高要求的电路,异步复位信号往往是需要的。当异步复位信号释放(即撤销复位),则有可能发生在时钟边沿附近,容易使寄存器输出出现亚稳态,因此必须对释放信号进行打拍同步处理。

module syn(

input clk,

input rstn,

output syn_rstn

);

reg rstn_r,rstn_rr; //寄存一拍和两拍

always@(posedge clk or negedge rstn) begin

if(!rstn) begin

rstn_r<=0;

rstn_rr<=0;

end

else begin

rstn_r<=rstn;

rstn_rr<=rstn_r;

end

assign syn_rstn = rstn_rr;

endmoduleQ:为什么是打两拍?

因为若出现亚稳态,打一拍过后仍然有输出亚稳态的风险,但在两拍过后,这种可能性非常低,也很少有需要打三拍的情况,因此打两拍处理是最常用的。

| 优点 | 缺点 | |

| 同步复位 | 利于仿真;利于时序分析;不会有复位毛刺 | 占用资源;在输入输出端口插入组合逻辑 |

| 异步复位 | 异步复位端口节约资源;时延低 | 异步逻辑易出现亚稳态;增加静态时序分析困难 |

2.门控时钟

在应用中,可能出现一段时间我们并不需要时钟,因此可以通过门控的方式将时钟信号置0,等待需要时再拉高,这能在很大程度上降低整体电路的功耗,节省资源。

时钟出现斩断/毛刺的原因:在时钟的高电平期间使能信号拉低,造成了斩断,如果下级电路对毛刺敏感,比如异步复位,就会影响电路工作的稳定性、可靠性,严重时会导致整个数字系统的逻辑紊乱。因此我们需要保证使能信号的跳变出现在时钟的低电平范围内,同理,需要对时钟的使能信号进行同步处理。

解决办法:加入下降沿敏感的触发器对使能信号同步。为什么是下降沿敏感呢?正如前面说的,我们要保证使能信号的跳变出现在时钟的低电平处,这样无论使能信号怎么变化,时钟的高电平处不会受到破坏。这样,电路的处理也很简单,在使能信号EN与clk相与之前,先让EN通过一个触发器同步到clk时域,再经过一个下降沿敏感的触发器后再和clk相与。这样就获得了一个尽可能消除亚稳态并且沿clk下降沿变化的EN信号,我们的门控时钟可靠性也得到了提高。

module steadyclk(

input clk,

input rstn,

input en,

output clko

);

reg en_r,en_rr;

always@(posedge clk or negedge rstn)

if(!rstn)

begin

en_r = 0;

en_rr = 0;

clko=0;

end

else

en_r = en;

end

always@(negedge clk or negedge rstn)

if(!rstn)

begin

en_rr = 0;

clko = 0;

end

else

en_rr = en_r;

end

assign clko=clk&en_rr;

endmodule

Q:能不能第一个DFF也设计成下降沿敏感呢?

可以,EN同步的关键在于第二个DFF一定要是下降沿敏感的,第一个DFF的作用是将EN先拉到clk时域,所以不管是上升沿还是下降沿都可以。

3.无毛刺时钟切换

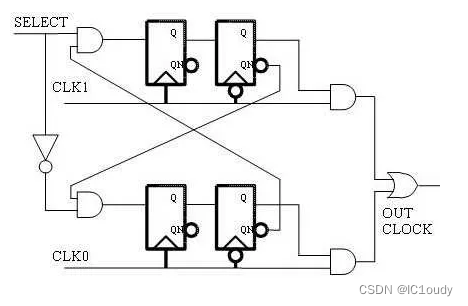

有了之前的分析后,无毛刺时钟切换的方法也跃然纸上:让选择信号SEL通过两个寄存器同步(其中后一个是下降沿敏感)后再与对应clk相与,对应电路如下:

注意:clk0和clk1是不同频的信号,同步时我们至多只能让它同步到其中一个时钟域。并且因为同步打拍延时的引入,当时钟选择切换后,也不是马上跳转为高电平。

Q:为什么第二级DFF的Q非需要接入输入?

Q非以负反馈的形式接回了输入,取与逻辑构建起clk0和clk1的关系,代表时钟切换前需要等一阵子,避免毛刺。